Materias

- Administración

- Agronomía

- Arquitectura

- Arte-Conservacion

- Ciencias Naturales

- Contabilidad

- Ciencias Sociales

- Derecho

- Deportes y Yoga

- Diseño

- Economía

- Ciencias Exactas y Astronomia

- GL

- Historia

- Hotelería turismo y protocolo

- Ingeniería

- Informática

- Lengua y Literatura

- Medicina

- Marketing

- Metodología

- Odontología

- Oficios Varios

- Pedagogia

- Psicología

- Química

- Tests

- Veterinaria

- Textos

- Comunicación

- Usted esta:

- Inicio

- Ingeniería Eléctrica

- Sistemas electrónicos digitales

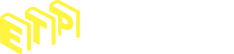

Sistemas electrónicos digitales

Autor: Mandado Pérez, Martín

ISBN: 9788426721983

Editorial: Marcombo, S.A.

Edición: 10

Páginas: 1070

Formato: 26x20x4

Cant. tomos: 1

Año: 2015

Idioma: España

Origen: España

Disponibilidad.:

Disponible

Gs 840.000

Incluye DVD

Cantidad:

Libros Relacionados

Esta nueva edición es el resultado del esfuerzo realizado por los dos autores para convertir el libro en un sistema de autoaprendizaje y adaptarlo a los cambios que los progresos alcanzados por la Microelectrónica en el siglo XX y en la primera década del siglo XXI exigen a la enseñanza y al aprendizaje de la Electrónica Digital.

La Electrónica Digital ha tenido un desarrollo espectacular desde que inició su andadura a finales de la década de 1950 hasta la actualidad, debido principalmente al extraordinario avance de la Microelectrónica. La superación de los diez millones de dispositivos en un único circuito integrado monolítico no solo supuso que los esquemas dejasen de constituir una herramienta válida para describir los sistemas digitales complejos, sino que trajo consigo el que algunos métodos de diseño y de implementación basados en su utilización se abandonasen y fuesen sustituidos por otros que utilizan como herramienta los lenguajes de descripción de sistemas digitales.

Lo expuesto anteriormente, unido a la tendencia, cada vez más acusada por parte de los fabricantes de circuitos integrados, a utilizar las herramientas de diseño asistido por computador para ocultar la forma de implementar el sistema físico (Hardware) y dificultar así la imitación por parte de sus competidores, hace que cada vez sea más difícil aprender los conceptos tecnológicos básicos de forma independiente de las soluciones concretas proporcionadas por aquellos. Los autores consideran que dicho aprendizaje es importante para formar técnicos que tengan capacidad de diseño de sistemas con circuitos integrados de diferentes fabricantes y, por ello, han desarrollado un considerable esfuerzo, basado en su experiencia profesional y docente, para combinar el análisis de los símbolos lógicos con los lenguajes de descripción de sistemas digitales. Dicho esfuerzo se plasma en esta décima edición en la que se propone el inicio del estudio del lenguaje VHDL en el capítulo 5, después de estudiar en el 3 y en el 4 los bloques funcionales combinacionales, y su ampliación en el capítulo 7, después de estudiar los bloques funcionales secuenciales en el capítulo 6.

Para superar los retos que todo ello supone se utiliza en este libro una estrategia basada en presentar los conceptos comenzando por los más sencillos hasta llegar a los más complejos, tal como propugna el versículo 63 del Tao Te King incluido en la portada interior del libro. Se hace uso para ello de los nuevos formatos electrónicos de almacenamiento de la información que permiten presentar en el papel los principios básicos de los circuitos que han dejado de ser utilizados, como por ejemplo los monoestables y los contadores asíncronos, e incluir una descripción más amplia en un apéndice dentro del disco compacto para aquel lector que quiera analizar con más detalle sus características con el objetivo de comprender por qué se dejaron de utilizar.

Esta edición está orientada a cumplir dos objetivos:

Proporcionar a los ingenieros de las diferentes áreas de las Tecnologías de la Información, como la Informática, la Electrónica y Automática Industriales y la Telecomunicación, los conocimientos básicos necesarios para trabajar en equipos multidisciplinares de diseño de sistemas digitales y colaborar con los científicos en el diseño de sistemas digitales complejos basados en el avance de la nanotecnología electrónica. Por primera vez en esta décima edición del libro se ponen ejemplos reales de productos no solo fabricados en España sino también desarrollados por empresas españolas e iberoamericanas para tratar de demostrar el camino a seguir para elevar la competitividad de nuestros países.

Proporcionar a los ingenieros electrónicos la base necesaria para convertirse en diseñadores del sistema físico de los sistemas digitales complejos.

La complejidad alcanzada por la Electrónica Digital hace que no exista un consenso general en lo que se refiere a las denominaciones de los diferentes circuitos y sistemas. Por ello, en el apéndice 10 se incluye un diccionario de términos en inglés y una propuesta de su equivalente en español, que trata de contribuir a mentalizar a los técnicos de habla hispana sobre la importancia de potenciar la utilización de nuestro idioma en todas las áreas de la Tecnología. Además, en el disco compacto se incluyen las hojas de características de numerosos circuitos integrados que muestran al lector la importancia que tiene aprender los conceptos de forma independiente de las denominaciones utilizadas por los distintos fabricantes.

Mención especial merece el capítulo 11 en el que se presentan los circuitos digitales configurables (Configurable integrated circuits) a través de numerosos ejemplos de circuitos integrados normalizados (Standard off the shelf) de distintos fabricantes, que tiene como objetivo introducir los circuitos que facilitan el diseño de sistemas electrónicos digitales de elevadas prestaciones.

La Electrónica Digital ha tenido un desarrollo espectacular desde que inició su andadura a finales de la década de 1950 hasta la actualidad, debido principalmente al extraordinario avance de la Microelectrónica. La superación de los diez millones de dispositivos en un único circuito integrado monolítico no solo supuso que los esquemas dejasen de constituir una herramienta válida para describir los sistemas digitales complejos, sino que trajo consigo el que algunos métodos de diseño y de implementación basados en su utilización se abandonasen y fuesen sustituidos por otros que utilizan como herramienta los lenguajes de descripción de sistemas digitales.

Lo expuesto anteriormente, unido a la tendencia, cada vez más acusada por parte de los fabricantes de circuitos integrados, a utilizar las herramientas de diseño asistido por computador para ocultar la forma de implementar el sistema físico (Hardware) y dificultar así la imitación por parte de sus competidores, hace que cada vez sea más difícil aprender los conceptos tecnológicos básicos de forma independiente de las soluciones concretas proporcionadas por aquellos. Los autores consideran que dicho aprendizaje es importante para formar técnicos que tengan capacidad de diseño de sistemas con circuitos integrados de diferentes fabricantes y, por ello, han desarrollado un considerable esfuerzo, basado en su experiencia profesional y docente, para combinar el análisis de los símbolos lógicos con los lenguajes de descripción de sistemas digitales. Dicho esfuerzo se plasma en esta décima edición en la que se propone el inicio del estudio del lenguaje VHDL en el capítulo 5, después de estudiar en el 3 y en el 4 los bloques funcionales combinacionales, y su ampliación en el capítulo 7, después de estudiar los bloques funcionales secuenciales en el capítulo 6.

Para superar los retos que todo ello supone se utiliza en este libro una estrategia basada en presentar los conceptos comenzando por los más sencillos hasta llegar a los más complejos, tal como propugna el versículo 63 del Tao Te King incluido en la portada interior del libro. Se hace uso para ello de los nuevos formatos electrónicos de almacenamiento de la información que permiten presentar en el papel los principios básicos de los circuitos que han dejado de ser utilizados, como por ejemplo los monoestables y los contadores asíncronos, e incluir una descripción más amplia en un apéndice dentro del disco compacto para aquel lector que quiera analizar con más detalle sus características con el objetivo de comprender por qué se dejaron de utilizar.

Esta edición está orientada a cumplir dos objetivos:

Proporcionar a los ingenieros de las diferentes áreas de las Tecnologías de la Información, como la Informática, la Electrónica y Automática Industriales y la Telecomunicación, los conocimientos básicos necesarios para trabajar en equipos multidisciplinares de diseño de sistemas digitales y colaborar con los científicos en el diseño de sistemas digitales complejos basados en el avance de la nanotecnología electrónica. Por primera vez en esta décima edición del libro se ponen ejemplos reales de productos no solo fabricados en España sino también desarrollados por empresas españolas e iberoamericanas para tratar de demostrar el camino a seguir para elevar la competitividad de nuestros países.

Proporcionar a los ingenieros electrónicos la base necesaria para convertirse en diseñadores del sistema físico de los sistemas digitales complejos.

La complejidad alcanzada por la Electrónica Digital hace que no exista un consenso general en lo que se refiere a las denominaciones de los diferentes circuitos y sistemas. Por ello, en el apéndice 10 se incluye un diccionario de términos en inglés y una propuesta de su equivalente en español, que trata de contribuir a mentalizar a los técnicos de habla hispana sobre la importancia de potenciar la utilización de nuestro idioma en todas las áreas de la Tecnología. Además, en el disco compacto se incluyen las hojas de características de numerosos circuitos integrados que muestran al lector la importancia que tiene aprender los conceptos de forma independiente de las denominaciones utilizadas por los distintos fabricantes.

Mención especial merece el capítulo 11 en el que se presentan los circuitos digitales configurables (Configurable integrated circuits) a través de numerosos ejemplos de circuitos integrados normalizados (Standard off the shelf) de distintos fabricantes, que tiene como objetivo introducir los circuitos que facilitan el diseño de sistemas electrónicos digitales de elevadas prestaciones.

Prólogo a la décima edición .VII

Introducción a la décima edición IX

Capítulo 1. Fundamentos de los sistemas digitales y códigos de numeración 1

1.1 Introducción 1

1.1.1 Señales eléctricas analógicas . 2

1.1.2 Señales eléctricas digitales . 3

1.1.3 Señales eléctricas temporales 5

1.2 Circuitos y sistemas electrónicos digitales y sus aplicaciones 6

1.3 Representación de los números. Sistemas de numeración .12

1.3.1 Introducción . 12

1.3.2 Sistema binario de numeración 13

1.3.3 Sistema octal de numeración . 15

1.3.4 Sistema hexadecimal de numeración 17

1.4 Códigos binarios .18

1.4.1 Códigos decimales codificados en binario 19

Códigos BCD ponderados 19

Códigos BCD no ponderados . 20

1.4.2 Códigos binarios continuos y cíclicos 21

1.4.3 Códigos alfanuméricos 24

1.4.4 Códigos para codificar estados internos y ejecutar acciones 27

1.4.5 Códigos detectores de errores 27

1.4.5.1 Introducción . 27

1.4.5.2 Detección de errores en la transmisión de información en paralelo . 28

1.4.5.3 Detección de errores en la transmisión de información en serie . 30

Detección de errores mediante bits de paridad 30

Detección de errores mediante suma . 32

Detección de errores mediante redundancia cíclica 33

1.4.6 Códigos correctores de errores 33

Capítulo 2. Álgebra de Boole y puertas lógicas 39

2.1 Definición y postulados . 39

2.2 Teoremas del álgebra de Boole 41

2.3 Función de un álgebra de Boole . 49

2.4 Tabla de verdad de una función lógica 55

2.5 Funciones lógicas importantes . 56

2.5.1 Función O-exclusiva 56

2.5.2 Función equivalencia o comparación . 57

2.6 Representación de una función lógica mediante un esquema de contactos 58

2.7 Puertas lógicas y su clasificación 61

2.7.1 Introducción . 61

2.7.2 Tipos de salida de las puertas lógicas 61

Salida normal 62

Salida de tres estados . 63

Salida de colector o drenador abierto 63

Salida de emisor o surtidor abierto 64

Salida con carga pasiva en el colector o en el drenador 64

Salida con carga pasiva en el emisor o en el surtidor . 65

Capítulo 3. Sistemas combinacionales 69

3.1 Generalidades 69

3.2 Simplificación de las funciones lógicas 71

3.2.1 Conceptos generales . 71

3.2.2 Método tabular de Karnaugh de simplificación de las funciones lógicas 72

3.2.3 Método numérico de Quine-McCluskey de simplificación de las funciones lógicas . 79

3.3 Definición y simplificación de las funciones incompletas . 79

3.4 Multifunciones: definición y aplicación de los métodos de simplificación 84

3.5 Implementación de las funciones lógicas mediante puertas lógicas . 87

3.5.1 Implementación con puertas NO-Y (NAND) y NO-O (NOR) . 87

3.5.2 Implementación de las funciones lógicas mediante la función «Y por conexión» 96

3.5.3 Implementación de las funciones lógicas con puertas O-exclusiva . 98

3.6 Fenómenos aleatorios en los sistemas combinacionales . 98

3.6.1 Introducción . 98

3.6.2 Fenómenos aleatorios estáticos . 98

3.6.3 Fenómenos aleatorios dinámicos . 99

3.6.4 Eliminación de los fenómenos aleatorios . 100

3.7 Bloques funcionales combinacionales de función fija 102

3.7.1 Introducción . 102

3.7.2 Decodificadores . 104

3.7.2.1 Introducción . 104

3.7.2.2 Decodificadores no excitadores 105

3.7.2.3 Decodificadores excitadores . 116

3.7.3 Codificadores . 124

3.7.4 Multiplexores 127

3.7.4.1 Multiplexores implementados con puertas Y y puertas O . 129

3.7.4.2 Multiplexores implementados con puertas triestado 134

3.7.4.3 Multiplexores implementados con interruptores . 137

3.7.4.4 Aplicaciones de los multiplexores . 140

3.7.5 Demultiplexores . 143

3.7.5.1 Demultiplexores implementados con decodificadores . 143

3.7.5.2 Demultiplexores implementados con interruptores . 144

3.7.6 Comparadores binarios . 145

3.7.7 Detectores/generadores de paridad . 150

3.7.8 Operadores aritméticos . 152

3.8 Bloques funcionales combinacionales programables 152

3.8.1 Introducción . 152

3.8.2 Bloques funcionales combinacionales programables no universales 154

3.8.3 Bloques funcionales combinacionales programables universales 154

3.8.3.1 Bloques funcionales combinacionales programables universales

completos. Memorias de acceso aleatorio 154

3.8.3.2 Bloques funcionales combinacionales programables universales

incompletos . 162

3.8.3.2.1 Matrices lógicas programables (PLA) 163

3.8.3.2.2 Matrices lógicas Y-programables (PAL) . 168

3.8.3.2.3 Ampliación de la capacidad de las matrices lógicas programables (PLA) y las matrices lógicas Y-programables (PAL) . 172

3.8.3.2.4 Matrices lógicas programables de puertas universales . 176

Capítulo 4. Operaciones y circuitos aritméticos 185

4.1 Generalidades .185

4.2 Operaciones en el sistema binario de numeración .185

4.2.1 Suma aritmética binaria . 186

4.2.2 Circuitos sumadores . 189

4.2.2.1 Circuito sumador secuencial . 189

4.2.2.2 Circuito sumador en paralelo . 190

Generación del acarreo en serie . 190

Generación del acarreo en paralelo 191

4.2.3 El circuito sumador total como bloque funcional . 199

4.2.3.1 Circuito comparador 199

4.2.3.2 Circuitos generadores/detectores de paridad . 199

Generador/detector de paridad en paralelo . 200

Generador/detector de paridad en serie 200

4.2.4 Resta binaria 201

4.2.4.1 Representación de los números negativos 201

4.2.4.2 Operación de resta con números negativos mediante el convenio

del complemento a dos . 204

4.2.4.3 Operación de resta con números negativos mediante el convenio

del complemento a uno . 210

4.2.5 Unidad aritmética y lógica . 216

4.2.6 Multiplicación binaria . 219

4.3 Operaciones aritméticas en los códigos decimales codificados

en binario (BCD) . 223

4.3.1 Introducción . 223

4.3.2 Operaciones aritméticas en el código decimal codificado en binario

natural (BCD natural) . 224

4.3.2.1 Suma en el código BCD natural 224

Sumador de números en BCD natural mediante un circuito combinacional 225

Sumador de números en BCD natural mediante un procesador digital secuencial 226

4.3.2.2 Resta en el código BCD natural 227

4.3.2.3 Suma y resta en el código BCD natural . 230

4.4 Formatos de representación de los números fraccionarios 232

4.4.1 Representación de los números fraccionarios en coma fija 232

4.4.2 Representación de los números fraccionarios en coma flotante 233

Capítulo 5. Introducción a los lenguajes de descripción de los sistemas digitales. Fundamentos del lenguaje VHDL . 239

5.1 Introducción 239

5.2 Fundamentos de los lenguajes de descripción de los sistemas digitales . 240

5.2.1 Introducción . 240

5.2.2 Principales elementos de un lenguaje RTL 240

5.3 Lenguajes de descripción de los sistemas digitales 242

5.3.1 Introducción . 242

5.3.2 Descripción de los sistemas digitales complejos 244

5.3.2.1 Descripción estructural 244

5.3.2.2 Descripción funcional 245

5.3.2.3 Descripción física o geométrica . 246

5.3.2.4 Descripción mixta 246

5.3.3 Conceptos generales de los lenguajes de descripción de los sistemas

digitales 246

5.3.4 Lenguajes HDL estructurados . 247

5.3.4.1 Introducción . 247

5.3.4.2 Características de los lenguajes HDL estructurados . 248

Introducción 248

Conceptos básicos de los lenguajes HDL estructurados . 249

Características de los archivos de descripción de los lenguajes HDL estructurados 249

5.4 Lenguaje VHDL de descripción de sistemas digitales . 250

5.4.1 Introducción . 250

5.4.2 Conceptos básicos del lenguaje VHDL 253

5.4.2.1 Identificadores y palabras reservadas . 253

5.4.2.2 Comentarios 254

5.4.2.3 Tipos de datos . 255

5.4.2.4 Objetos de datos 256

5.4.2.5 Atributos 258

5.4.2.6 Operadores predefinidos . 259

5.4.2.7 Componentes 260

5.4.3 Elementos básicos de la descripción de un sistema digital en VHDL 261

5.4.3.1 Definición de las bibliotecas 261

5.4.3.2 Definición básica de la entidad 261

5.4.3.3 Definición básica de la arquitectura 262

5.4.4 Descripción de los sistemas digitales en VHDL . 263

5.4.4.1 Descripción de flujo de datos de los sistemas digitales 264

5.4.4.1.1 Introducción . 264

5.4.4.1.2 Sentencias de asignación condicional de señales . 265

5.4.4.2 Descripción algorítmica de los sistemas digitales 268

5.4.4.2.1 Introducción . 268

5.4.4.2.2 Sentencias secuenciales 269

5.4.4.3 Descripción estructural de los sistemas digitales 274

5.4.5 Simulación de la descripción en VHDL de circuitos y sistemas digitales . 277

5.4.5.1 Introducción . 277

5.4.5.2 Generación de los estímulos de prueba 278

5.4.5.2.1 Definición de las señales de prueba 279

5.4.5.2.2 Programación de las señales de prueba 279

5.4.6 Descripción y simulación de sistemas combinacionales en VHDL . 281

5.4.6.1 Puertas lógicas 282

5.4.6.2 Funciones lógicas implementadas con puertas lógicas interconectadas . 284

5.4.6.3 Decodificadores . 284

5.4.6.4 Multiplexores . 286

5.4.6.5 Comparadores . 288

5.4.6.6 Operadores aritméticos . 289

Capítulo 6. Sistemas secuenciales . 293

6.1 Conceptos generales . 293

6.1.1 Fundamentos . 293

6.1.2 Diagrama de estados de un sistema secuencial 298

6.1.2.1 Especificación de un sistema secuencial mediante los niveles

de las variables de entrada 298

6.1.2.2 Especificación de un sistema secuencial mediante los flancos o cambios

de nivel de las variables de entrada . 302

6.2 Sistemas secuenciales asíncronos 313

6.2.1 Introducción . 313

6.2.2 Sistemas secuenciales asíncronos caracterizados mediante niveles 313

6.2.2.1 Sistemas secuenciales asíncronos de realimentación directa 313

6.2.2.2 Biestables asíncronos activados por niveles . 324

6.2.2.3 Diseño de los sistemas secuenciales asíncronos caracterizados por niveles con realimentación mediante biestables R-S 327

6.2.3 Sistemas secuenciales asíncronos caracterizados mediante flancos 328

6.2.4 Circuitos digitales temporales . 329

6.2.4.1 Introducción . 329

6.2.4.2 Circuitos temporizadores . 330

6.2.4.2.1 Monoestables 331

6.2.4.2.2 Temporizadores analógico-digitales 335

6.2.4.3 Generadores de impulsos 338

6.2.4.4 Aplicaciones de los circuitos digitales temporales 347

6.3 Sistemas secuenciales síncronos 351

6.3.1 Introducción . 351

6.3.2 Biestables sincronizados . 353

6.3.2.1 Introducción . 353

6.3.2.2 Biestables sincronizados mediante niveles . 355

6.3.2.3 Biestables sincronizados mediante cambios de nivel . 360

6.3.2.3.1 Biestables sincronizados por impulsos 361

6.3.2.3.2 Biestables sincronizados por flancos . 367

6.3.2.3.3 Biestables sincronizados por flancos con entrada de inhibición . 372

6.3.3 Representación gráfica de los biestables síncronos . 374

6.3.4 Sistemas secuenciales síncronos . 374

6.3.4.1 Introducción . 374

6.3.4.2 Sistemas secuenciales síncronos de aplicación general . 381

6.3.4.2.1 Registros de entrada y salida en paralelo 381

6.3.4.2.2 Contadores síncronos 382

6.3.4.2.3 Registros de desplazamiento . 387

6.3.4.3 Sistemas secuenciales síncronos asincronizados . 389

6.3.4.4 Bloques funcionales síncronos 391

6.3.4.4.1 Introducción . 391

6.3.4.4.2 Teoría general y símbolos normalizados 391

6.3.4.5 Contadores 399

6.3.4.5.1 Contadores síncronos 401

6.3.4.5.2 Aplicaciones de los contadores síncronos 412

6.3.4.6 Registros de desplazamiento 421

6.3.4.6.1 Conceptos generales . 421

6.3.4.6.2 Aplicaciones de los registros de desplazamiento 429

6.3.4.7 Registros de entrada y salida en paralelo 434

6.3.4.8 Conjuntos de registros . 437

6.3.5 Diseño de los sistemas secuenciales síncronos . 440

6.3.5.1 Clasificación de los sistemas secuenciales síncronos 441

6.3.5.2 Diseño de los sistemas secuenciales síncronos cableados 442

6.3.5.3 Diseño de los sistemas secuenciales síncronos programables 448

6.3.5.3.1 Sistemas secuenciales síncronos implementados con circuitos combinacionales programables completos . 449

6.3.5.3.2 Sistemas secuenciales síncronos programables implementados con circuitos combinacionales programables incompletos . 461

6.3.5.4 Sistemas secuenciales síncronos modulares 480

6.3.5.5 Sistemas secuenciales síncronos semimodulares 485

6.3.5.6 Aplicaciones de los sistemas secuenciales síncronos . 486

6.3.5.6.1 Introducción . 486

6.3.5.6.2 Controladores lógicos síncronos . 487

6.4 Representación gráfica de las señales de un sistema secuencial síncrono 497

6.4.1 Relaciones entre dos señales . 497

6.4.2 Relación entre varias señales 498

Capítulo 7. Conceptos y sentencias avanzadas del lenguaje VHDL 511

7.1 Introducción . 511

7.2 Tipos de datos 511

7.3 Sentencias adicionales del VHDL . 512

7.3.1 Otras formas de la sentencia WAIT . 512

7.3.2 Sentencias de generación . 515

7.3.3 Parámetros genéricos 517

7.3.4 Sentencias de control de la ejecución de bucles . 518

7.3.4.1 Sentencia LOOP 518

7.3.4.2 Sentencia FOR combinada con LOOP . 519

7.3.4.3 Sentencia WHILE combinada con LOOP 519

7.3.4.4 Sentencia EXIT . 521

7.3.4.5 Sentencia NEXT . 522

7.4 Subprogramas 523

7.4.1 Procedimientos 523

7.4.2 Funciones . 525

7.5 Descripción y simulación de bloques funcionales secuenciales en VHDL . 528

7.5.1 Biestables . 528

7.5.2 Registros de entrada y salida en paralelo sincronizados por flancos . 534

7.5.3 Contadores . 536

7.5.4 Registros de desplazamiento 542

7.6 Descripción y simulación de los sistemas secuenciales síncronos . 543

Capítulo 8. Tecnologías de implementación de los circuitos digitales .551

8.1 Introducción . 551

8.2 Características generales de los circuitos digitales . 553

Cargabilidad de salida (Fan-out) 553

Cargabilidad de entrada (Fan-in) 554

Tensión umbral (Threshold voltage) 554

Margen de ruido (Noise margin) 554

Curva de inmunidad dinámica al ruido . 555

Tiempo de propagación medio 556

Tensión de alimentación 556

Corriente de alimentación . 556

Potencia disipada 556

Producto potencia disipada-tiempo de propagación . 556

8.3 Circuitos digitales con diodos 557

8.4 Circuitos digitales con transistores . 559

8.4.1 Características principales del transistor bipolar en conmutación . 559

8.4.2 Circuitos digitales con componentes discretos. Tecnología resistencia-transistor . 562

8.4.3 Circuitos bloque de tecnología resistencia-transistor (RTL) 563

8.4.4 Circuitos integrados digitales . 563

8.4.4.1 Introducción . 563

8.4.4.2 Clasificación de los circuitos integrados digitales . 564

8.4.5 Circuitos integrados digitales monolíticos . 564

8.4.5.1 Introducción . 564

Clasificación según la implementación física 564

Clasificación según las características funcionales . 564

8.4.5.2 Clasificación de los CIDM según el tipo de semiconductor utilizado . 566

8.4.5.3 Clasificación de los CIDM según el número de dispositivos 566

8.4.5.4 Circuitos integrados de función fija . 569

8.4.5.4.1 Circuitos integrados de función fija normalizados de aplicación general 570

8.4.5.4.2 Circuitos integrados de función fija normalizados de aplicación específica . 571

8.4.5.4.3 Circuitos integrados de función fija especificados por el usuario . 572

Circuitos integrados ASIC totalmente a medida 573

Circuitos integrados ASIC semimedida . 573

8.4.5.5 Circuitos integrados de función variable . 576

8.4.5.5.1 CIDM normalizados programables 576

8.4.5.5.2 CIDM normalizados configurables . 579

Dispositivos lógicos programables (PLD) . 580

Conjuntos configurables de circuitos lógicos (FPGA) 584

8.4.6 Circuitos integrados digitales monolíticos y mixtos complejos 584

8.4.6.1 Circuitos híbridos de capa gruesa y fina . 586

8.4.6.2 Módulos integrados múltiples . 587

8.4.6.3 Sistemas en un único circuito integrado . 587

8.4.6.4 Sistemas microelectromecánicos 592

8.4.7 Circuitos integrados monolíticos digitales bipolares de silicio . 593

8.4.7.1 Tecnología resistencia-transistor 593

8.4.7.2 Tecnología diodo-transistor (DTL) 594

8.4.7.3 Tecnología transistor-transistor (TTL) 597

Características generales 597

Puertas lógicas TTL con salida de colector abierto 601

Puertas lógicas TTL con salida triestado . 602

8.4.7.4 Tecnología de alta inmunidad al ruido . 604

8.4.7.5 Tecnologías no saturadas 605

8.4.7.5.1 Tecnología TTL Schottky 605

8.4.7.5.2 Tecnología de acoplamiento por emisor (ECL) 606

8.4.7.6 Tecnología de inyección integrada . 606

8.4.8 Circuitos integrados monolíticos digitales con transistores MOS de silicio . 607

8.4.8.1 Introducción . 607

8.4.8.2 Fundamentos de los transistores MOS . 607

8.4.8.3 Circuitos digitales básicos implementados con transistores MOS . 614

8.4.8.4 Tecnologías digitales MOS 616

8.4.8.4.1 Tecnología MOS estática . 616

8.4.8.4.2 Tecnología MOS dinámica . 618

8.4.8.4.3 Tecnología CMOS 619

Conceptos generales . 619

Puertas CMOS de drenador abierto . 622

Puertas CMOS de tres estados . 622

Biestables CMOS . 623

Puertas CMOS de transmisión 624

Tecnología CMOS dinámica . 626

Resumen de las características de la tecnología CMOS . 627

8.4.9 Tecnología BiCMOS 627

8.4.10 Tecnología de arseniuro de galio (GaAs) . 630

8.4.10.1 Introducción 630

8.4.10.2 Dispositivos electrónicos de arseniuro de galio . 630

8.4.10.3 Puertas lógicas de tecnología arseniuro de galio . 631

8.5 Nanoelectrónica digital . 632

8.5.1 Introducción . 632

8.5.2 Dispositivos nanoelectrónicos 633

8.6 Encapsulado de los circuitos integrados 633

8.7 Zócalos de montaje . 636

8.8 Verificación de los circuitos integrados VLSI y ULSI 637

8.8.1 Introducción . 637

8.8.2 Diseño orientado a la verificabilidad . 639

8.8.2.1 Técnicas específicas para la verificación externa . 639

8.8.2.2 Técnicas estructuradas para la verificación externa . 641

8.8.2.3 Técnicas estructuradas para la autoverificación . 644

Capítulo 9. Unidades de memoria 653

9.1 Introducción 653

9.2 Capacidad de una memoria .654

9.3 Forma de acceder a la información 656

9.3.1 Memorias de acceso directo . 657

9.3.2 Memorias de acceso secuencial . 657

9.3.3 Memorias asociativas 658

9.4 Tecnologías de los elementos de memoria 658

9.4.1 Introducción . 658

9.4.1.1 Permanencia de la información . 659

9.4.1.2 Duración de la memorización 659

9.4.2 Elementos de memoria volátiles . 659

9.4.2.1 Elementos de memoria volátiles estáticos 659

9.4.2.2 Elementos de memoria volátiles dinámicos 660

9.4.3 Elementos de memoria no volátiles 661

9.4.3.1 Elementos reprogramables basados en transistores MOS . 661

9.4.3.1.1 Transistor MOS de puerta flotante borrable con rayos ultravioleta 661

9.4.3.1.2 Transistor MOS de puerta flotante y efecto túnel 662

9.4.3.1.3 Transistor MOS de puerta flotante de espesor del aislante reducido 663

9.4.3.2 Elementos reprogramables basados en materiales ferroeléctricos . 664

9.4.3.3 Elementos no reprogramables 665

9.4.3.3.1 Programables por máscara 665

9.4.3.3.2 Fusibles 666

9.4.3.3.3 Antifusibles 666

9.4.3.3.4 Programables una sola vez 667

9.5 Estructura interna de una memoria 667

9.5.1 Memorias de estructura interna aleatoria . 668

9.5.1.1 Características generales 668

9.5.1.2 Organización de las memorias de acceso aleatorio 672

9.5.1.2.1 Organización 2D 673

9.5.1.2.2 Organización 3D o por coincidencia 674

9.5.1.2.3 Organización 2½D . 676

9.5.1.3 Forma de realizar las operaciones de escritura y lectura de una memoria de acceso aleatorio 677

9.5.1.3.1 Memorias de acceso aleatorio de escritura y lectura no simultáneas 677

9.5.1.3.2 Memorias de acceso aleatorio de escritura y lectura simultáneas . 678

9.5.1.3.3 Memorias de acceso aleatorio múltiple . 679

9.5.1.4 Tecnologías de las memorias de acceso aleatorio 680

9.5.2 Memorias de estructura interna serie . 680

9.5.2.1 Características generales 680

9.5.2.2 Organización de las memorias serie 681

9.5.2.2.1 Organización en serie bit a bit 681

9.5.2.2.2 Organización en serie posición a posición . 682

9.5.2.3 Tecnologías de las memorias serie 683

9.6 Memorias de acceso directo 685

9.6.1 Memorias de acceso directo y estructura interna aleatoria 686

9.6.1.1 Características generales 686

9.6.1.2 Memorias de acceso aleatorio activas volátiles 687

9.6.1.2.1 Introducción . 687

9.6.1.2.2 Memorias activas estáticas de escritura y lectura no simultáneas (SRAM) 688

9.6.1.2.2.1 Memorias SRAM asíncronas . 688

9.6.1.2.2.2 Memorias SRAM síncronas . 695

9.6.1.2.2.3 Memorias SRAM síncronas de ráfagas (SBRAM) 699

9.6.1.2.3 Memorias activas dinámicas de escritura y lectura no simultáneas (DRAM) . 700

Fundamentos de las memorias DRAM . 700

Memorias DRAM avanzadas 708

9.6.1.2.4 Memorias activas volátiles asíncronas de escritura y lectura simultáneas . 713

9.6.1.2.5 Memorias activas volátiles asíncronas de acceso múltiple . 716

9.6.1.3 Memorias de acceso aleatorio asíncronas activas estáticas no volátiles . 720

9.6.1.3.1 Memorias SRAM con sistema de alimentación ininterrumpida . 720

9.6.1.3.2 Memorias de tecnología ferroeléctrica 721

9.6.1.4 Memorias de acceso aleatorio pasivas . 722

9.6.1.4.1 Memorias totalmente pasivas . 723

9.6.1.4.2 Memorias pasivas programables 725

9.6.1.4.3 Memorias pasivas reprogramables 725

9.6.1.4.3.1 Memorias pasivas borrables con rayos ultravioleta (EPROM) 726

9.6.1.4.3.2 Memorias pasivas reprogramables de efecto túnel (EEPROM) 732

9.6.1.4.3.3 Memorias pasivas flash . 737

9.6.1.5 Memorias de acceso aleatorio con comunicación serie . 741

9.6.1.5.1 Introducción . 741

9.6.1.5.2 Memorias activas no volátiles serie 742

9.6.1.5.3 Memorias EEPROM serie . 742

9.6.1.5.4 Memorias flash serie 744

9.6.1.6 Diseño de unidades de memoria de acceso aleatorio modulares con bloques funcionales . 746

9.6.1.6.1 Elevación del número de bits de cada posición 746

9.6.1.6.2 Elevación del número de posiciones . 747

9.6.1.6.3 Elevación del número de bits de cada posición y del número de posiciones 749

9.6.2 Memorias de acceso directo y estructura interna serie . 751

9.7 Memorias de acceso secuencial 756

9.7.1 Características generales 756

9.7.2 Registros de desplazamiento 757

9.7.2.1 Registros de desplazamiento estáticos . 757

9.7.2.2 Registros de desplazamiento dinámicos . 758

9.7.3 Memorias cola (FIFO) . 759

9.7.3.1 Memoria cola implementada con una memoria de estructura interna serie . 760

9.7.3.2 Memoria cola implementada con una memoria de estructura interna aleatoria 761

9.7.4 Memorias pila (LIFO) 765

9.7.4.1 Memoria pila implementada con una memoria de estructura interna serie 767

9.7.4.2 Memoria pila implementada con una memoria de estructura interna aleatoria 769

9.8 Memorias de acceso directo y secuencial 770

9.8.1 Conceptos generales . 770

9.8.2 Memorias circulares . 770

9.9 Memorias asociativas . 771

9.9.1 Descripción general . 771

9.9.2 Implementación del sistema físico 772

9.9.2.1 Implementación con un comparador por cada posición de memoria . 772

9.9.2.2 Implementación con una memoria de acceso aleatorio y un único comparador . 774

Capítulo 10. Procesadores digitales secuenciales síncronos .777

10.1 Introducción 777

10.2 Conceptos generales . 777

10.3 Sistema físico de la unidad operativa 789

10.3.1 Introducción . 789

10.3.2 Estructura de las unidades operativas . 797

10.3.2.1 Unidades operativas con registros y un solo bus 798

10.3.2.2 Unidades operativas con registros y dos buses 799

10.3.2.3 Unidades operativas con memoria de acceso aleatorio activa (RAM)

sincronizada por flancos y de acceso doble en lectura . 802

10.3.2.4 Unidades operativas con memoria de acceso aleatorio activa (RAM)

sincronizada por niveles y de acceso doble en lectura 805

10.3.2.5 Unidades operativas con circuito desplazador combinacional 808

10.3.2.6 Unidades operativas expansibles . 810

10.4 Sistema físico de la unidad de control . 813

10.4.1 Procesadores digitales secuenciales síncronos con unidad de control

de arquitectura Harvard . 813

10.4.2 Procesadores digitales secuenciales síncronos con unidad de control

de arquitectura Princeton 815

10.5 Circuitos de interfaz . 822

10.5.1 Fundamentos . 822

10.5.2 Forma de realizar la transferencia de información . 824

10.5.2.1 Puertos paralelo . 825

10.5.2.2 Puertos serie . 829

10.5.3 Convertidores de digital en analógico y de analógico en digital . 830

10.5.3.1 Introducción 830

10.5.3.2 Convertidores de digital en analógico . 832

10.5.3.3 Convertidores de analógico en digital 833

10.5.4 Forma de controlar la transferencia 834

10.6 Implementación de los procesadores digitales secuenciales síncronos programables 835

10.6.1 Introducción . 835

10.6.2 Computadores de aplicación general . 837

10.6.2.1 Introducción 837

10.6.2.2 Computadores monoprocesador . 839

10.6.2.2.1 Unidades operativas con capacidad de operación con números representados en coma flotante 839

10.6.2.2.2 Segmentación de las funciones aritméticas 840

10.6.2.2.3 Almacenamiento de las instrucciones en una memoria de acceso secuencial y solapamiento de la búsqueda

y ejecución de las instrucciones . 841

10.6.2.2.4 Memoria oculta 844

10.6.2.2.5 Computadores superescalares . 845

10.6.2.2.6 Ubicación automática de periféricos . 847

10.6.2.3 Procesadores digitales secuenciales síncronos implementados con varios procesadores 848

10.6.2.3.1 Introducción . 848

10.6.2.3.2 Sistemas multiprocesador . 849

10.6.2.3.3 Sistemas multicomputador 852

10.6.3 Computadores de aplicación específica 853

10.6.3.1 Microcontroladores . 853

10.6.3.1.1 Introducción . 853

10.6.3.1.2 Arquitectura de la unidad de control . 858

10.6.3.1.3 Capacidad de operación en paralelo 859

10.6.3.1.4 Capacidad de memoria 859

Memoria de datos 859

Memoria de instrucciones . 860

10.6.3.1.5 Circuitos de interfaz de entrada/salida y periféricos internos 860

10.6.3.1.5.1 Puertos paralelo 861

10.6.3.1.5.2 Puertos serie . 864

10.6.3.1.5.3 Circuitos de control de la transferencia 865

10.6.3.1.5.4 Periféricos internos 865

10.6.3.1.6 Desarrollo de sistemas basados en un microcontrolador 866

10.6.3.2 Autómatas programables . 866

10.6.3.2.1 Fundamentos de los autómatas programables 866

10.6.3.2.2 Recursos físicos (hardware) y de programación (software) . 872

10.6.3.2.2.1 Unidad Central 874

10.6.3.2.2.2 Capacidad de memoria de programa/datos 875

10.6.3.2.2.3 Capacidad de entradas y salidas digitales . 875

10.6.3.2.2.4 Modularidad de entradas y salidas 876

Autómatas programables totalmente modulares . 876

Autómatas programables semimodulares . 877

Autómatas programables compactos . 878

10.6.3.2.2.5 Módulos específicos de entrada/salida 879

10.6.3.2.2.6 Capacidad de interrupción 880

10.6.3.2.2.7 Interfaz máquina-usuario . 882

10.6.3.2.2.8 Recursos de Comunicaciones . 885

10.6.3.2.2.9 Seguridad ante sabotajes y seguridad ante averías . 885

10.6.3.2.2.10 Lenguajes de programación 886

10.6.3.3 Computadores industriales 886

10.6.3.4 Procesadores digitales de señales 888

10.6.3.4.1 Introducción . 888

10.6.3.4.2 Procesadores digitales de señales de coma fija 890

10.6.3.4.3 Procesadores digitales de señales de coma flotante . 892

10.6.3.4.4 Procesadores digitales de señales especializados 892

10.6.3.4.5 Procesadores digitales de señales de instrucciones

de gran tamaño 892

10.6.3.5 Computadores integrados de aplicación específica 893

10.6.3.5.1 Computadores integrados de aplicación específica de repertorio de instrucciones fijo . 893

10.6.3.5.2 Computadores integrados de aplicación específica de repertorio de instrucciones variable . 896

10.6.3.6 Procesadores digitales configurables 896

Capítulo 11. Introducción a los circuitos digitales configurables y sus aplicaciones .905

11.1 Introducción 905

11.2 Dispositivos lógicos programables 908

11.2.1 Introducción . 908

11.2.2 Dispositivos lógicos programables simples . 910

11.2.3 Dispositivos lógicos programables complejos . 919

11.2.3.1 Circuitos CPLD de asignación variable y segmentados 919

Circuitos CPLD de asignación variable . 919

Circuitos CPLD segmentados 919

Circuitos CPLD de asignación variable y segmentados 925

11.2.3.2 Circuitos CPLD de complejidad muy elevada 928

Circuitos CPLD implementados con macroceldas complejas . 931

Circuitos CPLD implementados con bloques lógicos complejos . 932

Circuitos CPLD implementados con recursos de interconexión distribuidos . 937

11.2.4 Tecnología de los circuitos PLD 938

11.2.4.1 Tecnología de fusibles 940

11.2.4.2 Tecnologías de transistores MOS . 940

11.2.4.3 Tecnologías de memoria activa estática 942

11.2.5 Configuración de los circuitos PLD 942

11.2.5.1 Circuitos PLD configurables fuera del sistema 943

11.2.5.2 Circuitos PLD configurables en el sistema . 943

11.2.6 Diseño e implementación de sistemas electrónicos con dispositivos

lógicos programables 945

11.2.6.1 Descripción . 945

11.2.6.2 Simulación funcional 946

11.2.6.3 Configuración del circuito PLD . 947

11.2.6.4 Simulación temporal . 947

11.2.6.5 Implementación y prueba 948

11.2.6.6 Diagrama detallado del proceso de diseño 949

11.3 Conjuntos configurables de puertas (FPGA) . 950

11.3.1 Introducción . 950

11.3.2 Organización de los recursos lógicos . 953

11.3.2.1 FPGA de organización del tipo terraza 953

11.3.2.2 FPGA de organización del tipo cuadrícula . 954

11.3.2.3 FPGA de organización del tipo mar de puertas . 955

11.3.3 Bloques lógicos internos . 956

11.3.3.1 Bloques lógicos internos configurables sencillos 957

11.3.3.2 Bloques lógicos internos configurables complejos 958

11.3.3.2.1 Bloques lógicos internos configurables basados en multiplexores 958

11.3.3.2.2 Bloques lógicos internos configurables basados en tablas de consulta 959

11.3.3.3 Bloques lógicos internos complejos de función fija . 964

Unidades de memoria 964

Circuitos aritméticos . 964

Procesadores digitales . 965

Controladores de comunicaciones . 965

Circuitos de sincronización y distribución del reloj 965

11.3.4 Bloques lógicos de entrada/salida . 965

11.3.5 Canales de interconexión . 969

11.3.5.1 Canales de interconexión directos . 969

11.3.5.2 Canales de interconexión indirectos 970

11.3.5.3 Unión de canales de interconexión 970

11.3.6 Recursos de sincronización y distribución del reloj . 971

11.3.6.1 Estabilidad del generador de impulsos 972

11.3.6.2 Tensión de alimentación del generador de impulsos . 973

11.3.6.3 Pendiente de cambio del generador de impulsos 973

11.3.6.4 Sincronización de las variables de entrada . 974

11.3.6.5 Distribución del reloj . 974

Distribución del reloj mediante amplificadores de impedancia de salida reducida 974

Distribución del reloj mediante bucles de fase enclavada . 975

Distribución del reloj mediante bucles de retardo enclavado 979

11.3.7 Tecnología de los interruptores programables . 980

11.3.7.1 Introducción 980

11.3.7.2 Circuitos FPGA del tipo SRAM . 981

11.3.7.3 Circuitos FPGA del tipo Flash 981

11.3.7.4 Circuitos FPGA del tipo antifusible . 981

11.3.8 Configuración de los circuitos FPGA 981

11.3.9 Diseño e implementación de sistemas digitales con circuitos FPGA . 983

11.3.9.1 Introducción 983

11.3.9.2 Diagrama detallado del proceso de diseño 983

11.3.10 Procesadores digitales configurables 989

11.3.10.1 Procesadores digitales configurables definidos mediante el sistema físico 990

11.3.10.2 Procesadores digitales configurables definidos mediante una herramienta de programación . 992

11.3.10.2.1 Procesadores digitales configurables de aplicación específica 992

11.3.10.2.2 Procesadores digitales programables configurables de repertorio de instrucciones fijo 1003

11.3.10.2.3 Procesadores digitales configurables programables de repertorio de instrucciones flexible 1005

Apéndice 1. Símbolos lógicos normalizados .1011

A1.1 Introducción 1011

A1.2 Símbolo gráfico normalizado 1012

A1.3 Símbolos asociados a las entradas y a las salidas . 1014

A1.4 Representación normalizada de los sistemas combinacionales 1017

A1.4.1 Generalidades . 1017

A1.4.2 Puertas lógicas 1017

A1.4.3 Símbolos de bloques funcionales combinacionales . 1018

A1.4.3.1 Relación G de dependencia Y (AND) . 1020

A1.4.3.2 Relación V de dependencia O (OR) 1021

A1.4.3.3 Relación N de inversión (Negate) . 1021

A1.4.3.4 Relación EN de desinhibición (Enable)/Inhibición (Disable) 1022

A1.4.3.5 Relación M de modo de operación (Mode) 1022

A1.4.3.6 Relación Z de conexión 1023

A1.4.3.7 Relación A de direccionamiento (Addressing) 1023

A1.4.3.8 Combinación de relaciones de dependencia . 1024

Combinación de simultaneidad 1024

Combinación de exclusión . 1025

A1.5 Representación normalizada de los sistemas secuenciales . 1025

A1.5.1 Generalidades . 1025

A1.5.2 Indicativos de los sistemas secuenciales 1026

A1.5.3 Relaciones de dependencia en sistemas secuenciales 1027

A1.5.3.1 Relaciones R de puesta a cero y S de puesta a uno 1027

A1.5.3.2 Relación C de control . 1028

De control por nivel 1028

De control por flanco 1028

A1.5.3.3 Relación M de modo de operación 1029

A1.5.3.4 Combinación de relaciones de dependencia . 1030

Combinación de simultaneidad 1030

Combinación de exclusión . 1030

A1.5.4 Ejemplos prácticos de sistemas secuenciales 1032

A1.5.4.1 Biestables síncronos 1032

A1.5.4.2 Registros de entrada y salida en paralelo 1033

A1.5.4.3 Contadores . 1037

Contadores asíncronos 1037

Contadores síncronos 1039

A1.5.4.4 Registros de desplazamiento . 1042

Apéndice 2. Sistemas digitales combinacionales

Está en el disco compacto e incluye el análisis de diversos métodos de diseño utilizados en el pasado y los que se incorporaron a las herramientas de diseño asistido por computador. Sus principales apartados son:

A2.1 Simplificación de las funciones lógicas complejas mediante las tablas de Karnaugh

A2.2 Fenómenos aleatorios estáticos de tipo uno y dinámicos en circuitos combinacionales

A2.3 Método numérico de minimización de las funciones lógicas

A2.4 Implementación de las funciones lógicas con circuitos del nivel superior

a dos compuestos por puertas NO-Y (NAND) y NO-O (NOR)

A2.5 Sistemas combinacionales programables no universales

A2.6 Circuitos operadores en BCD natural

A2.7 Implementación de las funciones lógicas con puertas O-exclusiva

Apéndice 3. Sistemas digitales secuenciales

Está en el disco compacto e incluye diversos métodos de análisis y de diseño de los sistemas secuenciales, que se utilizaron cuando los sistemas digitales se implementaban con componentes discretos y con circuitos integrados de escala de integración pequeña y mediana. Sus principales apartados son:

A3.1 Diseño de sistemas secuenciales asíncronos de realimentación directa

A3.2 Biestables asíncronos caracterizados mediante niveles

A3.3 Circuitos temporizadores implementados con monoestables

A3.4 Circuitos generadores de impulsos implementados con monoestables

A3.5 Biestables sincronizados mediante flancos

A3.6 Biestables asíncronos activados por flancos

A3.7 Sistemas secuenciales caracterizados por flancos e implementados con biestables asíncronos activados por flancos

A3.8 Símbolos normalizados de los biestables sincronizados por flancos y de las celdas CAF

A3.9 Sistemas secuenciales síncronos asincronizados

A3.10 Características de los bloques funcionales síncronos

A3.11 Sistemas secuenciales síncronos cableados implementados con biestables sincronizados por flancos

Apéndice 4. Circuitos temporales analógico-digitales

Está en el disco compacto y sus principales apartados son:

A2.1 Introducción

A4.2 Circuito temporal analógico-digital multifuncional 555

A4.3 Circuito temporal analógico-digital multifuncional 556

A4.4 Circuito temporal analógico-digital 558

Apéndice 5. Tecnologías de circuitos integrados bipolares

Está en el disco compacto e incluye diversas tecnologías que están obsoletas porque han sido superadas por otras que poseen mejores características como por ejemplo, consumir menos energía, ocupar memos área de silicio, funcionar a mayores frecuencias, etc.

Sus principales apartados son:

A5.1 Introducción

A5.2 Tecnología de inmunidad al ruido elevada

A5.3 Tecnología de acoplamiento por emisor (ECL)

A5.4 Tecnología de inyección integrada

Apéndice 6. Convertidores digital-analógicos y analógico-digitales

Está en el disco compacto y se incluyó en el capítulo 9 de la séptima edición. Sus principales apartados

son:

A6.1 Introducción

A6.2 Convertidores digital-analógicos

A6.3 Convertidores analógico-digitales

Apéndice 7. A mpliación de los dispositivos lógicos programables simples y complejos

Está en el disco compacto y amplía la información sobre los dispositivos lógicos programables incluida

en el capítulo 11. Sus principales apartados son:

A7.1 Introducción

A7.2 Ampliación de los dispositivos lógicos programables simples

A7.3 Ampliación de los dispositivos lógicos programables complejos

A7.4 Dispositivos lógicos programables de Lattice

A7.5 Dispositivos lógicos programables de Xilinx

A7.6 Dispositivos lógicos programables de Altera

Apéndice 8. Lenguajes HDL no estructurados

Está en el disco compacto y amplia la información sobre los lenguajes no estructurados de descripción

de los sistemas digitales que se introducen en el apartado 5.3.3 del capítulo 5. Sus principales

apartados son:

A8.1 Características generales y evolución

A8.2 Lenguaje ABEL

Apéndice 9. Lista de acrónimos en inglés

Está en el disco compacto.

Apéndice 10. P ropuesta de equivalencias de términos de electrónica digital

entre el inglés y el español 1045

Índice alfabético en inglés y español 1047

Introducción a la décima edición IX

Capítulo 1. Fundamentos de los sistemas digitales y códigos de numeración 1

1.1 Introducción 1

1.1.1 Señales eléctricas analógicas . 2

1.1.2 Señales eléctricas digitales . 3

1.1.3 Señales eléctricas temporales 5

1.2 Circuitos y sistemas electrónicos digitales y sus aplicaciones 6

1.3 Representación de los números. Sistemas de numeración .12

1.3.1 Introducción . 12

1.3.2 Sistema binario de numeración 13

1.3.3 Sistema octal de numeración . 15

1.3.4 Sistema hexadecimal de numeración 17

1.4 Códigos binarios .18

1.4.1 Códigos decimales codificados en binario 19

Códigos BCD ponderados 19

Códigos BCD no ponderados . 20

1.4.2 Códigos binarios continuos y cíclicos 21

1.4.3 Códigos alfanuméricos 24

1.4.4 Códigos para codificar estados internos y ejecutar acciones 27

1.4.5 Códigos detectores de errores 27

1.4.5.1 Introducción . 27

1.4.5.2 Detección de errores en la transmisión de información en paralelo . 28

1.4.5.3 Detección de errores en la transmisión de información en serie . 30

Detección de errores mediante bits de paridad 30

Detección de errores mediante suma . 32

Detección de errores mediante redundancia cíclica 33

1.4.6 Códigos correctores de errores 33

Capítulo 2. Álgebra de Boole y puertas lógicas 39

2.1 Definición y postulados . 39

2.2 Teoremas del álgebra de Boole 41

2.3 Función de un álgebra de Boole . 49

2.4 Tabla de verdad de una función lógica 55

2.5 Funciones lógicas importantes . 56

2.5.1 Función O-exclusiva 56

2.5.2 Función equivalencia o comparación . 57

2.6 Representación de una función lógica mediante un esquema de contactos 58

2.7 Puertas lógicas y su clasificación 61

2.7.1 Introducción . 61

2.7.2 Tipos de salida de las puertas lógicas 61

Salida normal 62

Salida de tres estados . 63

Salida de colector o drenador abierto 63

Salida de emisor o surtidor abierto 64

Salida con carga pasiva en el colector o en el drenador 64

Salida con carga pasiva en el emisor o en el surtidor . 65

Capítulo 3. Sistemas combinacionales 69

3.1 Generalidades 69

3.2 Simplificación de las funciones lógicas 71

3.2.1 Conceptos generales . 71

3.2.2 Método tabular de Karnaugh de simplificación de las funciones lógicas 72

3.2.3 Método numérico de Quine-McCluskey de simplificación de las funciones lógicas . 79

3.3 Definición y simplificación de las funciones incompletas . 79

3.4 Multifunciones: definición y aplicación de los métodos de simplificación 84

3.5 Implementación de las funciones lógicas mediante puertas lógicas . 87

3.5.1 Implementación con puertas NO-Y (NAND) y NO-O (NOR) . 87

3.5.2 Implementación de las funciones lógicas mediante la función «Y por conexión» 96

3.5.3 Implementación de las funciones lógicas con puertas O-exclusiva . 98

3.6 Fenómenos aleatorios en los sistemas combinacionales . 98

3.6.1 Introducción . 98

3.6.2 Fenómenos aleatorios estáticos . 98

3.6.3 Fenómenos aleatorios dinámicos . 99

3.6.4 Eliminación de los fenómenos aleatorios . 100

3.7 Bloques funcionales combinacionales de función fija 102

3.7.1 Introducción . 102

3.7.2 Decodificadores . 104

3.7.2.1 Introducción . 104

3.7.2.2 Decodificadores no excitadores 105

3.7.2.3 Decodificadores excitadores . 116

3.7.3 Codificadores . 124

3.7.4 Multiplexores 127

3.7.4.1 Multiplexores implementados con puertas Y y puertas O . 129

3.7.4.2 Multiplexores implementados con puertas triestado 134

3.7.4.3 Multiplexores implementados con interruptores . 137

3.7.4.4 Aplicaciones de los multiplexores . 140

3.7.5 Demultiplexores . 143

3.7.5.1 Demultiplexores implementados con decodificadores . 143

3.7.5.2 Demultiplexores implementados con interruptores . 144

3.7.6 Comparadores binarios . 145

3.7.7 Detectores/generadores de paridad . 150

3.7.8 Operadores aritméticos . 152

3.8 Bloques funcionales combinacionales programables 152

3.8.1 Introducción . 152

3.8.2 Bloques funcionales combinacionales programables no universales 154

3.8.3 Bloques funcionales combinacionales programables universales 154

3.8.3.1 Bloques funcionales combinacionales programables universales

completos. Memorias de acceso aleatorio 154

3.8.3.2 Bloques funcionales combinacionales programables universales

incompletos . 162

3.8.3.2.1 Matrices lógicas programables (PLA) 163

3.8.3.2.2 Matrices lógicas Y-programables (PAL) . 168

3.8.3.2.3 Ampliación de la capacidad de las matrices lógicas programables (PLA) y las matrices lógicas Y-programables (PAL) . 172

3.8.3.2.4 Matrices lógicas programables de puertas universales . 176

Capítulo 4. Operaciones y circuitos aritméticos 185

4.1 Generalidades .185

4.2 Operaciones en el sistema binario de numeración .185

4.2.1 Suma aritmética binaria . 186

4.2.2 Circuitos sumadores . 189

4.2.2.1 Circuito sumador secuencial . 189

4.2.2.2 Circuito sumador en paralelo . 190

Generación del acarreo en serie . 190

Generación del acarreo en paralelo 191

4.2.3 El circuito sumador total como bloque funcional . 199

4.2.3.1 Circuito comparador 199

4.2.3.2 Circuitos generadores/detectores de paridad . 199

Generador/detector de paridad en paralelo . 200

Generador/detector de paridad en serie 200

4.2.4 Resta binaria 201

4.2.4.1 Representación de los números negativos 201

4.2.4.2 Operación de resta con números negativos mediante el convenio

del complemento a dos . 204

4.2.4.3 Operación de resta con números negativos mediante el convenio

del complemento a uno . 210

4.2.5 Unidad aritmética y lógica . 216

4.2.6 Multiplicación binaria . 219

4.3 Operaciones aritméticas en los códigos decimales codificados

en binario (BCD) . 223

4.3.1 Introducción . 223

4.3.2 Operaciones aritméticas en el código decimal codificado en binario

natural (BCD natural) . 224

4.3.2.1 Suma en el código BCD natural 224

Sumador de números en BCD natural mediante un circuito combinacional 225

Sumador de números en BCD natural mediante un procesador digital secuencial 226

4.3.2.2 Resta en el código BCD natural 227

4.3.2.3 Suma y resta en el código BCD natural . 230

4.4 Formatos de representación de los números fraccionarios 232

4.4.1 Representación de los números fraccionarios en coma fija 232

4.4.2 Representación de los números fraccionarios en coma flotante 233

Capítulo 5. Introducción a los lenguajes de descripción de los sistemas digitales. Fundamentos del lenguaje VHDL . 239

5.1 Introducción 239

5.2 Fundamentos de los lenguajes de descripción de los sistemas digitales . 240

5.2.1 Introducción . 240

5.2.2 Principales elementos de un lenguaje RTL 240

5.3 Lenguajes de descripción de los sistemas digitales 242

5.3.1 Introducción . 242

5.3.2 Descripción de los sistemas digitales complejos 244

5.3.2.1 Descripción estructural 244

5.3.2.2 Descripción funcional 245

5.3.2.3 Descripción física o geométrica . 246

5.3.2.4 Descripción mixta 246

5.3.3 Conceptos generales de los lenguajes de descripción de los sistemas

digitales 246

5.3.4 Lenguajes HDL estructurados . 247

5.3.4.1 Introducción . 247

5.3.4.2 Características de los lenguajes HDL estructurados . 248

Introducción 248

Conceptos básicos de los lenguajes HDL estructurados . 249

Características de los archivos de descripción de los lenguajes HDL estructurados 249

5.4 Lenguaje VHDL de descripción de sistemas digitales . 250

5.4.1 Introducción . 250

5.4.2 Conceptos básicos del lenguaje VHDL 253

5.4.2.1 Identificadores y palabras reservadas . 253

5.4.2.2 Comentarios 254

5.4.2.3 Tipos de datos . 255

5.4.2.4 Objetos de datos 256

5.4.2.5 Atributos 258

5.4.2.6 Operadores predefinidos . 259

5.4.2.7 Componentes 260

5.4.3 Elementos básicos de la descripción de un sistema digital en VHDL 261

5.4.3.1 Definición de las bibliotecas 261

5.4.3.2 Definición básica de la entidad 261

5.4.3.3 Definición básica de la arquitectura 262

5.4.4 Descripción de los sistemas digitales en VHDL . 263

5.4.4.1 Descripción de flujo de datos de los sistemas digitales 264

5.4.4.1.1 Introducción . 264

5.4.4.1.2 Sentencias de asignación condicional de señales . 265

5.4.4.2 Descripción algorítmica de los sistemas digitales 268

5.4.4.2.1 Introducción . 268

5.4.4.2.2 Sentencias secuenciales 269

5.4.4.3 Descripción estructural de los sistemas digitales 274

5.4.5 Simulación de la descripción en VHDL de circuitos y sistemas digitales . 277

5.4.5.1 Introducción . 277

5.4.5.2 Generación de los estímulos de prueba 278

5.4.5.2.1 Definición de las señales de prueba 279

5.4.5.2.2 Programación de las señales de prueba 279

5.4.6 Descripción y simulación de sistemas combinacionales en VHDL . 281

5.4.6.1 Puertas lógicas 282

5.4.6.2 Funciones lógicas implementadas con puertas lógicas interconectadas . 284

5.4.6.3 Decodificadores . 284

5.4.6.4 Multiplexores . 286

5.4.6.5 Comparadores . 288

5.4.6.6 Operadores aritméticos . 289

Capítulo 6. Sistemas secuenciales . 293

6.1 Conceptos generales . 293

6.1.1 Fundamentos . 293

6.1.2 Diagrama de estados de un sistema secuencial 298

6.1.2.1 Especificación de un sistema secuencial mediante los niveles

de las variables de entrada 298

6.1.2.2 Especificación de un sistema secuencial mediante los flancos o cambios

de nivel de las variables de entrada . 302

6.2 Sistemas secuenciales asíncronos 313

6.2.1 Introducción . 313

6.2.2 Sistemas secuenciales asíncronos caracterizados mediante niveles 313

6.2.2.1 Sistemas secuenciales asíncronos de realimentación directa 313

6.2.2.2 Biestables asíncronos activados por niveles . 324

6.2.2.3 Diseño de los sistemas secuenciales asíncronos caracterizados por niveles con realimentación mediante biestables R-S 327

6.2.3 Sistemas secuenciales asíncronos caracterizados mediante flancos 328

6.2.4 Circuitos digitales temporales . 329

6.2.4.1 Introducción . 329

6.2.4.2 Circuitos temporizadores . 330

6.2.4.2.1 Monoestables 331

6.2.4.2.2 Temporizadores analógico-digitales 335

6.2.4.3 Generadores de impulsos 338

6.2.4.4 Aplicaciones de los circuitos digitales temporales 347

6.3 Sistemas secuenciales síncronos 351

6.3.1 Introducción . 351

6.3.2 Biestables sincronizados . 353

6.3.2.1 Introducción . 353

6.3.2.2 Biestables sincronizados mediante niveles . 355

6.3.2.3 Biestables sincronizados mediante cambios de nivel . 360

6.3.2.3.1 Biestables sincronizados por impulsos 361

6.3.2.3.2 Biestables sincronizados por flancos . 367

6.3.2.3.3 Biestables sincronizados por flancos con entrada de inhibición . 372

6.3.3 Representación gráfica de los biestables síncronos . 374

6.3.4 Sistemas secuenciales síncronos . 374

6.3.4.1 Introducción . 374

6.3.4.2 Sistemas secuenciales síncronos de aplicación general . 381

6.3.4.2.1 Registros de entrada y salida en paralelo 381

6.3.4.2.2 Contadores síncronos 382

6.3.4.2.3 Registros de desplazamiento . 387

6.3.4.3 Sistemas secuenciales síncronos asincronizados . 389

6.3.4.4 Bloques funcionales síncronos 391

6.3.4.4.1 Introducción . 391

6.3.4.4.2 Teoría general y símbolos normalizados 391

6.3.4.5 Contadores 399

6.3.4.5.1 Contadores síncronos 401

6.3.4.5.2 Aplicaciones de los contadores síncronos 412

6.3.4.6 Registros de desplazamiento 421

6.3.4.6.1 Conceptos generales . 421

6.3.4.6.2 Aplicaciones de los registros de desplazamiento 429

6.3.4.7 Registros de entrada y salida en paralelo 434

6.3.4.8 Conjuntos de registros . 437

6.3.5 Diseño de los sistemas secuenciales síncronos . 440

6.3.5.1 Clasificación de los sistemas secuenciales síncronos 441

6.3.5.2 Diseño de los sistemas secuenciales síncronos cableados 442

6.3.5.3 Diseño de los sistemas secuenciales síncronos programables 448

6.3.5.3.1 Sistemas secuenciales síncronos implementados con circuitos combinacionales programables completos . 449

6.3.5.3.2 Sistemas secuenciales síncronos programables implementados con circuitos combinacionales programables incompletos . 461

6.3.5.4 Sistemas secuenciales síncronos modulares 480

6.3.5.5 Sistemas secuenciales síncronos semimodulares 485

6.3.5.6 Aplicaciones de los sistemas secuenciales síncronos . 486

6.3.5.6.1 Introducción . 486

6.3.5.6.2 Controladores lógicos síncronos . 487

6.4 Representación gráfica de las señales de un sistema secuencial síncrono 497

6.4.1 Relaciones entre dos señales . 497

6.4.2 Relación entre varias señales 498

Capítulo 7. Conceptos y sentencias avanzadas del lenguaje VHDL 511

7.1 Introducción . 511

7.2 Tipos de datos 511

7.3 Sentencias adicionales del VHDL . 512

7.3.1 Otras formas de la sentencia WAIT . 512

7.3.2 Sentencias de generación . 515

7.3.3 Parámetros genéricos 517

7.3.4 Sentencias de control de la ejecución de bucles . 518

7.3.4.1 Sentencia LOOP 518

7.3.4.2 Sentencia FOR combinada con LOOP . 519

7.3.4.3 Sentencia WHILE combinada con LOOP 519

7.3.4.4 Sentencia EXIT . 521

7.3.4.5 Sentencia NEXT . 522

7.4 Subprogramas 523

7.4.1 Procedimientos 523

7.4.2 Funciones . 525

7.5 Descripción y simulación de bloques funcionales secuenciales en VHDL . 528

7.5.1 Biestables . 528

7.5.2 Registros de entrada y salida en paralelo sincronizados por flancos . 534

7.5.3 Contadores . 536

7.5.4 Registros de desplazamiento 542

7.6 Descripción y simulación de los sistemas secuenciales síncronos . 543

Capítulo 8. Tecnologías de implementación de los circuitos digitales .551

8.1 Introducción . 551

8.2 Características generales de los circuitos digitales . 553

Cargabilidad de salida (Fan-out) 553

Cargabilidad de entrada (Fan-in) 554

Tensión umbral (Threshold voltage) 554

Margen de ruido (Noise margin) 554

Curva de inmunidad dinámica al ruido . 555

Tiempo de propagación medio 556

Tensión de alimentación 556

Corriente de alimentación . 556

Potencia disipada 556

Producto potencia disipada-tiempo de propagación . 556

8.3 Circuitos digitales con diodos 557

8.4 Circuitos digitales con transistores . 559

8.4.1 Características principales del transistor bipolar en conmutación . 559

8.4.2 Circuitos digitales con componentes discretos. Tecnología resistencia-transistor . 562

8.4.3 Circuitos bloque de tecnología resistencia-transistor (RTL) 563

8.4.4 Circuitos integrados digitales . 563

8.4.4.1 Introducción . 563

8.4.4.2 Clasificación de los circuitos integrados digitales . 564

8.4.5 Circuitos integrados digitales monolíticos . 564

8.4.5.1 Introducción . 564

Clasificación según la implementación física 564

Clasificación según las características funcionales . 564

8.4.5.2 Clasificación de los CIDM según el tipo de semiconductor utilizado . 566

8.4.5.3 Clasificación de los CIDM según el número de dispositivos 566

8.4.5.4 Circuitos integrados de función fija . 569

8.4.5.4.1 Circuitos integrados de función fija normalizados de aplicación general 570

8.4.5.4.2 Circuitos integrados de función fija normalizados de aplicación específica . 571

8.4.5.4.3 Circuitos integrados de función fija especificados por el usuario . 572

Circuitos integrados ASIC totalmente a medida 573

Circuitos integrados ASIC semimedida . 573

8.4.5.5 Circuitos integrados de función variable . 576

8.4.5.5.1 CIDM normalizados programables 576

8.4.5.5.2 CIDM normalizados configurables . 579

Dispositivos lógicos programables (PLD) . 580

Conjuntos configurables de circuitos lógicos (FPGA) 584

8.4.6 Circuitos integrados digitales monolíticos y mixtos complejos 584

8.4.6.1 Circuitos híbridos de capa gruesa y fina . 586

8.4.6.2 Módulos integrados múltiples . 587

8.4.6.3 Sistemas en un único circuito integrado . 587

8.4.6.4 Sistemas microelectromecánicos 592

8.4.7 Circuitos integrados monolíticos digitales bipolares de silicio . 593

8.4.7.1 Tecnología resistencia-transistor 593

8.4.7.2 Tecnología diodo-transistor (DTL) 594

8.4.7.3 Tecnología transistor-transistor (TTL) 597

Características generales 597

Puertas lógicas TTL con salida de colector abierto 601

Puertas lógicas TTL con salida triestado . 602

8.4.7.4 Tecnología de alta inmunidad al ruido . 604

8.4.7.5 Tecnologías no saturadas 605

8.4.7.5.1 Tecnología TTL Schottky 605

8.4.7.5.2 Tecnología de acoplamiento por emisor (ECL) 606

8.4.7.6 Tecnología de inyección integrada . 606

8.4.8 Circuitos integrados monolíticos digitales con transistores MOS de silicio . 607

8.4.8.1 Introducción . 607

8.4.8.2 Fundamentos de los transistores MOS . 607

8.4.8.3 Circuitos digitales básicos implementados con transistores MOS . 614

8.4.8.4 Tecnologías digitales MOS 616

8.4.8.4.1 Tecnología MOS estática . 616

8.4.8.4.2 Tecnología MOS dinámica . 618

8.4.8.4.3 Tecnología CMOS 619

Conceptos generales . 619

Puertas CMOS de drenador abierto . 622

Puertas CMOS de tres estados . 622

Biestables CMOS . 623

Puertas CMOS de transmisión 624

Tecnología CMOS dinámica . 626

Resumen de las características de la tecnología CMOS . 627

8.4.9 Tecnología BiCMOS 627

8.4.10 Tecnología de arseniuro de galio (GaAs) . 630

8.4.10.1 Introducción 630

8.4.10.2 Dispositivos electrónicos de arseniuro de galio . 630

8.4.10.3 Puertas lógicas de tecnología arseniuro de galio . 631

8.5 Nanoelectrónica digital . 632

8.5.1 Introducción . 632

8.5.2 Dispositivos nanoelectrónicos 633

8.6 Encapsulado de los circuitos integrados 633

8.7 Zócalos de montaje . 636

8.8 Verificación de los circuitos integrados VLSI y ULSI 637

8.8.1 Introducción . 637

8.8.2 Diseño orientado a la verificabilidad . 639

8.8.2.1 Técnicas específicas para la verificación externa . 639

8.8.2.2 Técnicas estructuradas para la verificación externa . 641

8.8.2.3 Técnicas estructuradas para la autoverificación . 644

Capítulo 9. Unidades de memoria 653

9.1 Introducción 653

9.2 Capacidad de una memoria .654

9.3 Forma de acceder a la información 656

9.3.1 Memorias de acceso directo . 657

9.3.2 Memorias de acceso secuencial . 657

9.3.3 Memorias asociativas 658

9.4 Tecnologías de los elementos de memoria 658

9.4.1 Introducción . 658

9.4.1.1 Permanencia de la información . 659

9.4.1.2 Duración de la memorización 659

9.4.2 Elementos de memoria volátiles . 659

9.4.2.1 Elementos de memoria volátiles estáticos 659

9.4.2.2 Elementos de memoria volátiles dinámicos 660

9.4.3 Elementos de memoria no volátiles 661

9.4.3.1 Elementos reprogramables basados en transistores MOS . 661

9.4.3.1.1 Transistor MOS de puerta flotante borrable con rayos ultravioleta 661

9.4.3.1.2 Transistor MOS de puerta flotante y efecto túnel 662

9.4.3.1.3 Transistor MOS de puerta flotante de espesor del aislante reducido 663

9.4.3.2 Elementos reprogramables basados en materiales ferroeléctricos . 664

9.4.3.3 Elementos no reprogramables 665

9.4.3.3.1 Programables por máscara 665

9.4.3.3.2 Fusibles 666

9.4.3.3.3 Antifusibles 666

9.4.3.3.4 Programables una sola vez 667

9.5 Estructura interna de una memoria 667

9.5.1 Memorias de estructura interna aleatoria . 668

9.5.1.1 Características generales 668

9.5.1.2 Organización de las memorias de acceso aleatorio 672

9.5.1.2.1 Organización 2D 673

9.5.1.2.2 Organización 3D o por coincidencia 674

9.5.1.2.3 Organización 2½D . 676

9.5.1.3 Forma de realizar las operaciones de escritura y lectura de una memoria de acceso aleatorio 677

9.5.1.3.1 Memorias de acceso aleatorio de escritura y lectura no simultáneas 677

9.5.1.3.2 Memorias de acceso aleatorio de escritura y lectura simultáneas . 678

9.5.1.3.3 Memorias de acceso aleatorio múltiple . 679

9.5.1.4 Tecnologías de las memorias de acceso aleatorio 680

9.5.2 Memorias de estructura interna serie . 680

9.5.2.1 Características generales 680

9.5.2.2 Organización de las memorias serie 681

9.5.2.2.1 Organización en serie bit a bit 681

9.5.2.2.2 Organización en serie posición a posición . 682

9.5.2.3 Tecnologías de las memorias serie 683

9.6 Memorias de acceso directo 685

9.6.1 Memorias de acceso directo y estructura interna aleatoria 686

9.6.1.1 Características generales 686

9.6.1.2 Memorias de acceso aleatorio activas volátiles 687

9.6.1.2.1 Introducción . 687

9.6.1.2.2 Memorias activas estáticas de escritura y lectura no simultáneas (SRAM) 688

9.6.1.2.2.1 Memorias SRAM asíncronas . 688

9.6.1.2.2.2 Memorias SRAM síncronas . 695

9.6.1.2.2.3 Memorias SRAM síncronas de ráfagas (SBRAM) 699

9.6.1.2.3 Memorias activas dinámicas de escritura y lectura no simultáneas (DRAM) . 700

Fundamentos de las memorias DRAM . 700

Memorias DRAM avanzadas 708

9.6.1.2.4 Memorias activas volátiles asíncronas de escritura y lectura simultáneas . 713

9.6.1.2.5 Memorias activas volátiles asíncronas de acceso múltiple . 716

9.6.1.3 Memorias de acceso aleatorio asíncronas activas estáticas no volátiles . 720

9.6.1.3.1 Memorias SRAM con sistema de alimentación ininterrumpida . 720

9.6.1.3.2 Memorias de tecnología ferroeléctrica 721

9.6.1.4 Memorias de acceso aleatorio pasivas . 722

9.6.1.4.1 Memorias totalmente pasivas . 723

9.6.1.4.2 Memorias pasivas programables 725

9.6.1.4.3 Memorias pasivas reprogramables 725

9.6.1.4.3.1 Memorias pasivas borrables con rayos ultravioleta (EPROM) 726

9.6.1.4.3.2 Memorias pasivas reprogramables de efecto túnel (EEPROM) 732

9.6.1.4.3.3 Memorias pasivas flash . 737

9.6.1.5 Memorias de acceso aleatorio con comunicación serie . 741

9.6.1.5.1 Introducción . 741

9.6.1.5.2 Memorias activas no volátiles serie 742

9.6.1.5.3 Memorias EEPROM serie . 742

9.6.1.5.4 Memorias flash serie 744

9.6.1.6 Diseño de unidades de memoria de acceso aleatorio modulares con bloques funcionales . 746

9.6.1.6.1 Elevación del número de bits de cada posición 746

9.6.1.6.2 Elevación del número de posiciones . 747

9.6.1.6.3 Elevación del número de bits de cada posición y del número de posiciones 749

9.6.2 Memorias de acceso directo y estructura interna serie . 751

9.7 Memorias de acceso secuencial 756

9.7.1 Características generales 756

9.7.2 Registros de desplazamiento 757

9.7.2.1 Registros de desplazamiento estáticos . 757

9.7.2.2 Registros de desplazamiento dinámicos . 758

9.7.3 Memorias cola (FIFO) . 759

9.7.3.1 Memoria cola implementada con una memoria de estructura interna serie . 760

9.7.3.2 Memoria cola implementada con una memoria de estructura interna aleatoria 761

9.7.4 Memorias pila (LIFO) 765

9.7.4.1 Memoria pila implementada con una memoria de estructura interna serie 767

9.7.4.2 Memoria pila implementada con una memoria de estructura interna aleatoria 769

9.8 Memorias de acceso directo y secuencial 770

9.8.1 Conceptos generales . 770

9.8.2 Memorias circulares . 770

9.9 Memorias asociativas . 771

9.9.1 Descripción general . 771

9.9.2 Implementación del sistema físico 772

9.9.2.1 Implementación con un comparador por cada posición de memoria . 772

9.9.2.2 Implementación con una memoria de acceso aleatorio y un único comparador . 774

Capítulo 10. Procesadores digitales secuenciales síncronos .777

10.1 Introducción 777

10.2 Conceptos generales . 777

10.3 Sistema físico de la unidad operativa 789

10.3.1 Introducción . 789

10.3.2 Estructura de las unidades operativas . 797

10.3.2.1 Unidades operativas con registros y un solo bus 798

10.3.2.2 Unidades operativas con registros y dos buses 799

10.3.2.3 Unidades operativas con memoria de acceso aleatorio activa (RAM)

sincronizada por flancos y de acceso doble en lectura . 802

10.3.2.4 Unidades operativas con memoria de acceso aleatorio activa (RAM)

sincronizada por niveles y de acceso doble en lectura 805

10.3.2.5 Unidades operativas con circuito desplazador combinacional 808

10.3.2.6 Unidades operativas expansibles . 810

10.4 Sistema físico de la unidad de control . 813

10.4.1 Procesadores digitales secuenciales síncronos con unidad de control

de arquitectura Harvard . 813

10.4.2 Procesadores digitales secuenciales síncronos con unidad de control

de arquitectura Princeton 815

10.5 Circuitos de interfaz . 822

10.5.1 Fundamentos . 822

10.5.2 Forma de realizar la transferencia de información . 824

10.5.2.1 Puertos paralelo . 825

10.5.2.2 Puertos serie . 829

10.5.3 Convertidores de digital en analógico y de analógico en digital . 830

10.5.3.1 Introducción 830

10.5.3.2 Convertidores de digital en analógico . 832

10.5.3.3 Convertidores de analógico en digital 833

10.5.4 Forma de controlar la transferencia 834

10.6 Implementación de los procesadores digitales secuenciales síncronos programables 835

10.6.1 Introducción . 835

10.6.2 Computadores de aplicación general . 837

10.6.2.1 Introducción 837

10.6.2.2 Computadores monoprocesador . 839

10.6.2.2.1 Unidades operativas con capacidad de operación con números representados en coma flotante 839

10.6.2.2.2 Segmentación de las funciones aritméticas 840

10.6.2.2.3 Almacenamiento de las instrucciones en una memoria de acceso secuencial y solapamiento de la búsqueda

y ejecución de las instrucciones . 841

10.6.2.2.4 Memoria oculta 844

10.6.2.2.5 Computadores superescalares . 845

10.6.2.2.6 Ubicación automática de periféricos . 847

10.6.2.3 Procesadores digitales secuenciales síncronos implementados con varios procesadores 848

10.6.2.3.1 Introducción . 848

10.6.2.3.2 Sistemas multiprocesador . 849

10.6.2.3.3 Sistemas multicomputador 852

10.6.3 Computadores de aplicación específica 853

10.6.3.1 Microcontroladores . 853

10.6.3.1.1 Introducción . 853

10.6.3.1.2 Arquitectura de la unidad de control . 858

10.6.3.1.3 Capacidad de operación en paralelo 859

10.6.3.1.4 Capacidad de memoria 859

Memoria de datos 859

Memoria de instrucciones . 860

10.6.3.1.5 Circuitos de interfaz de entrada/salida y periféricos internos 860

10.6.3.1.5.1 Puertos paralelo 861

10.6.3.1.5.2 Puertos serie . 864

10.6.3.1.5.3 Circuitos de control de la transferencia 865

10.6.3.1.5.4 Periféricos internos 865

10.6.3.1.6 Desarrollo de sistemas basados en un microcontrolador 866

10.6.3.2 Autómatas programables . 866

10.6.3.2.1 Fundamentos de los autómatas programables 866

10.6.3.2.2 Recursos físicos (hardware) y de programación (software) . 872

10.6.3.2.2.1 Unidad Central 874

10.6.3.2.2.2 Capacidad de memoria de programa/datos 875

10.6.3.2.2.3 Capacidad de entradas y salidas digitales . 875